# INTERSIL IM6100 CMOS 12 BIT MICROPROCESSOR

#

# **CONTENTS**

| Introduction                                  | . 2  |

|-----------------------------------------------|------|

| Section I: Intersil IM6100 CMOS               |      |

| 12-Bit Microprocessor                         |      |

| Introduction                                  | . 4  |

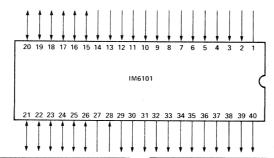

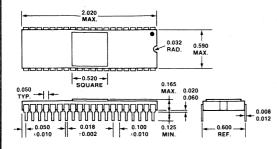

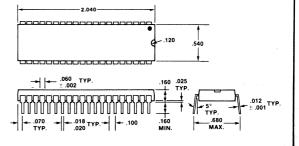

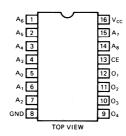

| Pin Assignments                               | . 6  |

| Specifications                                | . 7  |

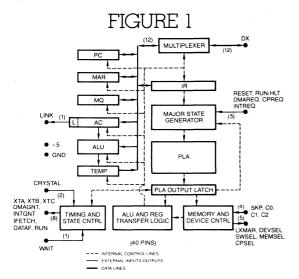

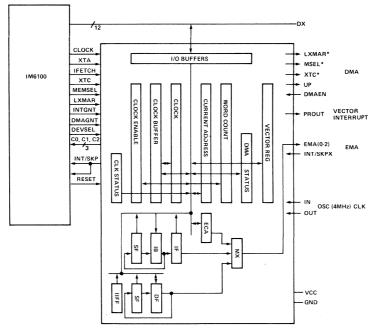

| Architecture                                  | . 8  |

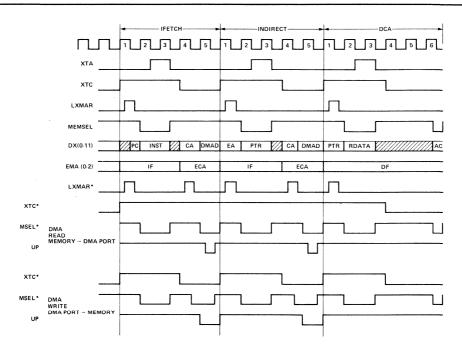

| Memory and Processor Instructions             | . 10 |

| Operate Instructions                          | . 12 |

| Input/Output Transfer Instructions            | . 16 |

| Internal Priority Structure                   | 21   |

| Applications                                  | 24   |

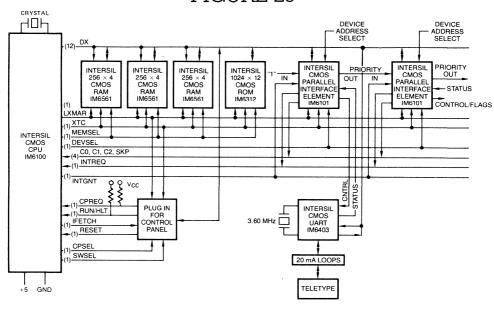

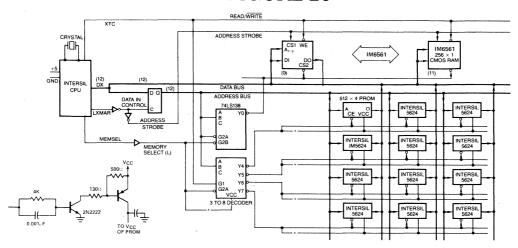

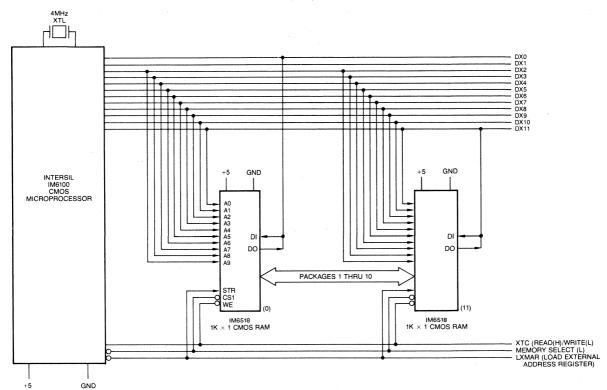

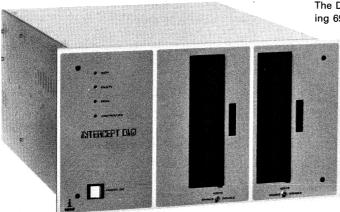

| Section II: Intercept Prototyping System      | 27   |

| Introduction                                  | . 28 |

| Specifications                                | 29   |

| Intercept Modules                             | 30   |

| Software and Hardware Options                 | . 32 |

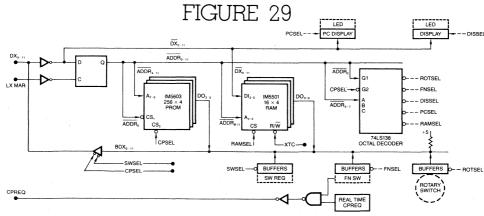

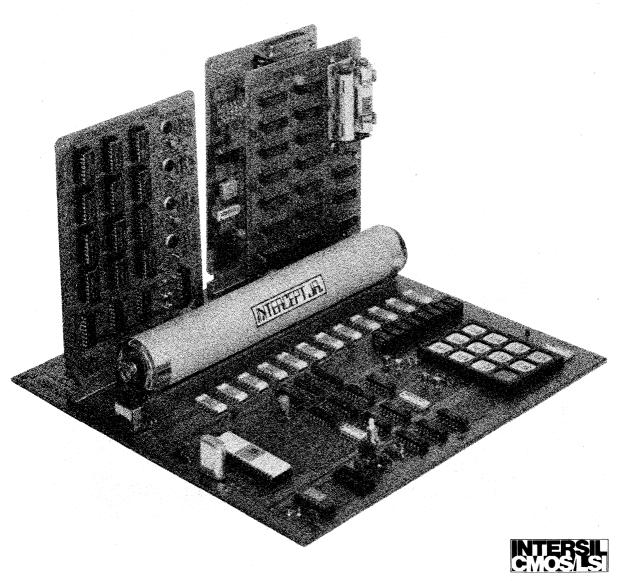

| Section III: Intercept Jr. Tutorial System    | 35   |

| Section IV: Intersil Data Sheets              | 41   |

| IM6101/6101A CMOS Parallel Interface Element  | 42   |

| IM6102 Memory Extention/DMA/Interval Timer/   |      |

| Controller (Medic)                            | 57   |

| IM6312/6312A CMOS ROM, 1024 Words x 12 Bits . | . 77 |

| IM6402/6403 CMOS/LSI UART                     | 81   |

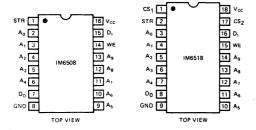

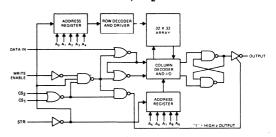

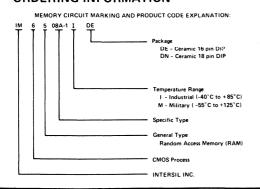

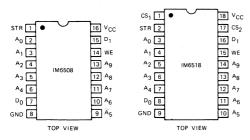

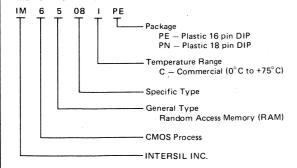

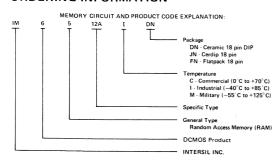

| IM6508/6518 CMOS RAM, 1024 Bit                |      |

| IM6508C/6518C CMOS RAM, 1024 Bit              |      |

| IM6512/6512A CMOS RAM, 768 Bit                |      |

| IM6523 CMOS Silicon Gate RAM, 256 Bit         | 101  |

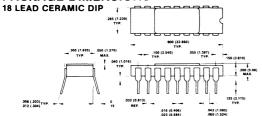

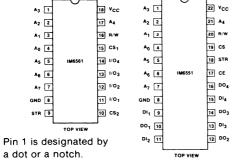

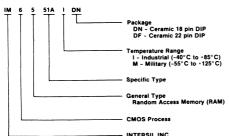

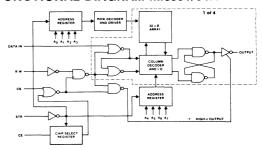

| IM6551/6561 CMOS RAM, 1024 Bit                | 105  |

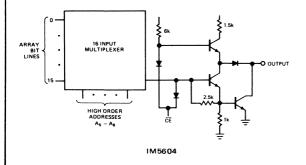

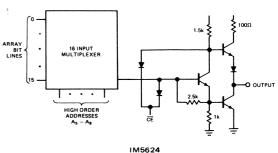

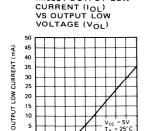

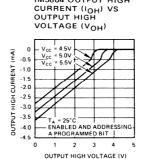

| IM5604/5624 Bipolar Programmable ROM          | 109  |

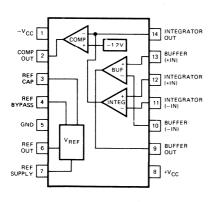

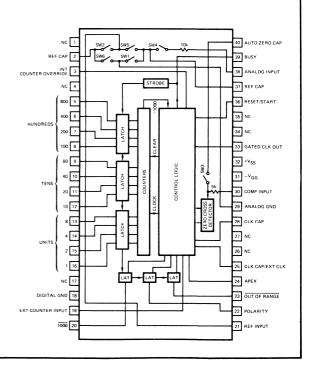

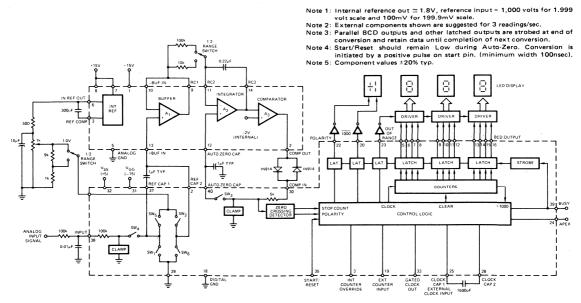

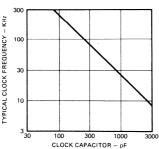

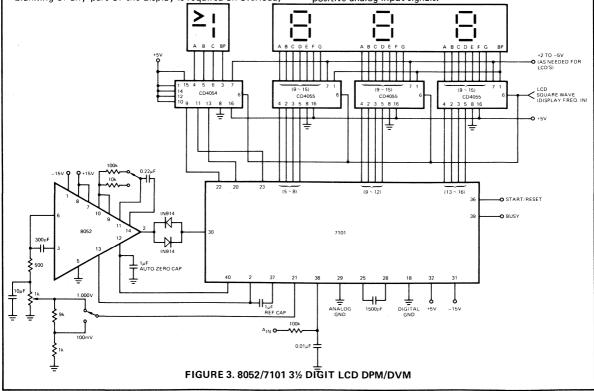

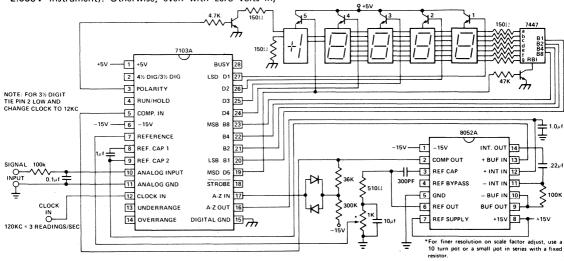

| 8052/7101 — 3½ Digit A/D Pair                 | 113  |

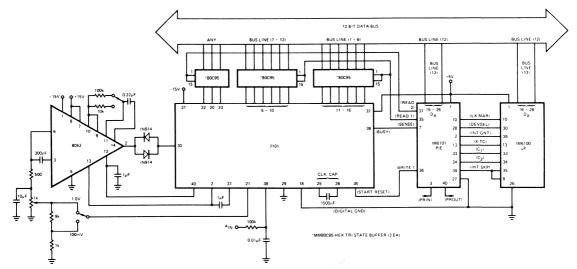

| 8052A/7103A - 4½ Digit Pair                   | 121  |

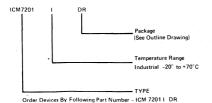

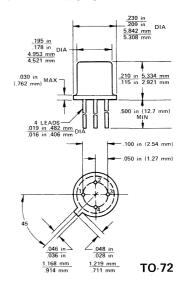

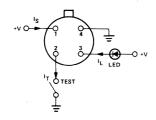

| ICM7201 Low Battery Voltage Indicator         | 129  |

| Continue V. CMOC DAM Delicities Day           | 404  |

# INTRODUCTION

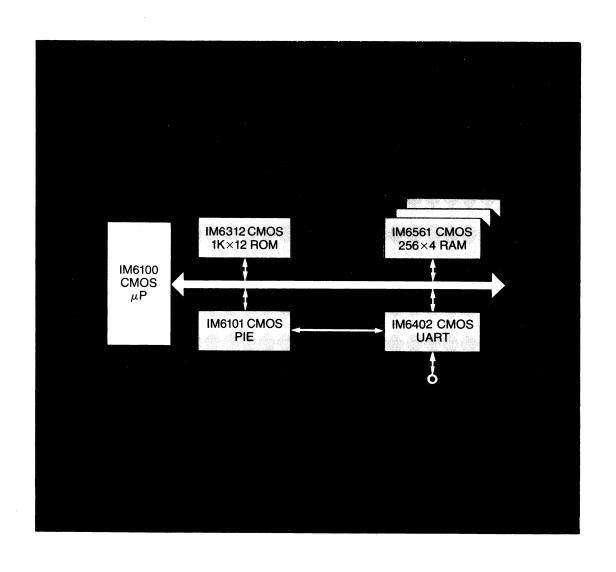

Since its founding on July 26, 1967, Intersil, Inc. has become a company of many products and processes.

In addition to the digital CMOS devices covered in detail in this publication, Intersil has developed and markets a line of advanced linear products and semiconductor memories. TTL bipolar, MOS, metal-gate CMOS and silicon-gate CMOS processes are all represented in Intersil's line, with the significant design advantage that, because they were developed by a single forward-thinking company, many of the different kinds of devices and technologies produced by Intersil will work together for enhanced performance and greater efficiency and flexibility of the final developed product.

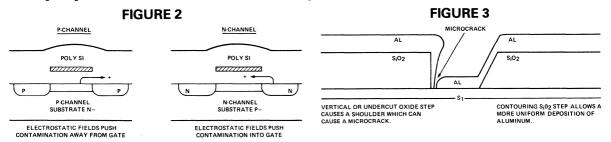

The Silicon Gate CMOS process, which was developed at Intersil over two years ago, offers a semiconductor structure resulting in packing densities which surpass the conventional metal gate process 3:1. Additionally, circuit performance is improved 2:1.

Mass production experience with the Silicon Gate CMOS process, through previously announced 256 and 1024 bit CMOS RAMs, has lead to the practicality of introducing the IM6100 microprocessor.

The IM6100 and IM6100A are single address, fixed word length, parallel transfer microprocessors using 12-bit, two's complement arithmetic. The processors recognize the instruction set of Digital Equipment Corporation's PDP-8/e minicomputer. The internal circuitry is completely static and is designed to operate at any speed between DC and the maximum operating frequency. Two pins are available to allow for an external crystal thereby eliminating the need for clock generators and level translators. The crystal can be removed and the processor clocked by an external clock generator. A 12-bit memory-accumulator ADD instruction is performed in 5µsec by the IM6100 using a +5 volt supply and in 2.5µsec by the IM6100A using a +10 volt supply. The device design is optimized to minimize the number of external components required for interfacing with standard memory and peripheral devices.

Intersil cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Intersil product. No other circuit patent licenses are implied. Intersil reserves the right to change without notice at any time the circuitry and specifications of any Intersil product represented in this document.

SECTION I: INTERSIL IM6100 CMOS 12 BIT MICROPROCESSOR

# INTRODUCTION

# IM6100 MICROPROCESSOR

Since its founding on July 26, 1967, INTERSIL INC. has offered its customers advanced products utilizing the semiconductor industry's most technologically sophisticated processes for the manufacture of practical, economical devices.

The Silicon Gate CMOS process, which was developed at Intersil in 1972, offers a semiconductor structure resulting in packing densities which surpass the conventional metal gate process 3:1. Additionally, circuit performance is improved 2:1.

Mass production experience with the Silicon Gate CMOS process, through previously announced 256 and 1024 bit CMOS RAMs, has lead to the practicality of introducing the IM6100 microprocessor.

The IM6100 is a single address, fixed word length, parallel transfer microprocessor using 12-bit, two's complement arithmetic. The processors recognize the instruction set of Digital Equipment Corporation's PDP-8/e minicomputer. The internal circuitry is completely static and is designed to operate at any speed between DC and the maximum operating frequency. Two pins are available to allow for an external crystal thereby eliminating the need for clock generators and level translators. The crystal can be removed and the processor clocked by an external clock generator. A 12-bit memory-accumulator ADD instruction, using a +5 volt supply, is performed in 5 $\mu$ sec by the IM6100A using a +10 volt supply. The device design is optimized to minimize the number of external components required for interfacing with standard memory and peripheral devices.

# **FEATURES**

#### DESIGN

- Silicon Gate Complementary MOS

- Fully Static-0 to 8 MHz

- Single Power Supply

IM6100/C V<sub>CC</sub> = 5 volts

IM6100A V<sub>CC</sub> = 10 volts

- Crystal Controlled On Chip Timing

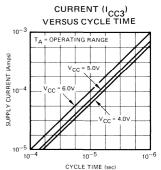

- Low Power Dissipation < 10mW @ 4 MHz @ 5 volts

- Single Power Supply 4V ≤ V<sub>CC</sub> ≤ 11V

- TTL Compatible at 5 volts

- Excellent Noise Immunity

- -55°C to +125°C Operation

#### **INTERFACE**

- Memory Any Speed

- Control Panel

- Switch Register

- Asynchronous CPU Memory and CPU Device Communication

- 64 I/O Devices with PDP-8/e Compatible Interface

- Device Controlled Input-Output

- All Control Signals Produced By The CPU

- Power-on Initialize

#### **ARCHITECTURAL**

- Executes PDP-8/e, Instruction Set

- Direct, Indirect, and Autoindexed Memory Addressing

- 12-Bit Memory Accumulator ADD Instruction IM6100 5μsec @ +5 volts/4.0 MHz

- IM6100A 2.5μsec @ +10 volts/8.0 MHz

IM6100C 6μsec @ +5 volts/3.3 MHz

- Input-Output Instruction

- IM6100 8.5µsec @ +5 volts/4.0 MHz IM6100A 4.25µsec @ +10 volts/8 MHz IM6100C 10.2µsec @ +5 volts/3.3 MHz

- Single-Clock, Single-Instruction Capability

- Direct Memory Access (DMA)

- Interrupt

- Dedicated Control Pane! Features

# **APPLICATIONS**

- Intelligent Computer Terminals

- POS Terminals

- Portable Terminals

- Aerospace/Satellite System

- Automotive Systems

- Remote Data Acquisition Systems

- Process Control

- Instrumentation

- Medical Electronics

- Displays

- Traffic Control

- Navigation

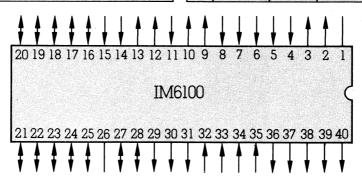

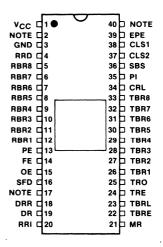

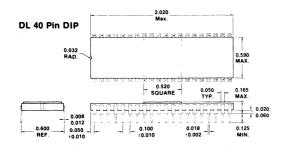

# PINASSIGNMENTS

| PIN | SYMBOL          | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                              |

|-----|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>cc</sub> |                 | Supply voltage.                                                                                                                                                          |

| 2   | RÜN             | Н               | The signal indicates the runstate of the CPU and may be used to power down the external circuitry                                                                        |

| 3   | DMAGNT          | Н               | Direct Memory Access Grant—DX lines are three-state.                                                                                                                     |

| 4   | DMAREQ          | L               | Direct Memory Access Request—DMA is granted at the end of the current instruction. Upon DMA grant, the CPU suspends program execution until the DMAREQ line is released. |

| 5   | CPREQ           | L               | Control Panel Request—a dedicated in-<br>terrupt which bypasses the normal<br>device interrupt request structure.                                                        |

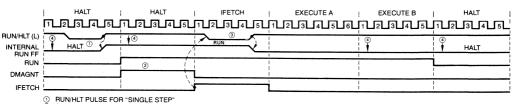

| 6   | RUN/HLT         | L L             | Pulsing the Run/Halt line causes the<br>CPU to alternately run and halt by<br>changing the state of the internal<br>RUN/HLT flip flop.                                   |

| 7   | RESET           | L               | Clears the AC and loads 7777 <sub>s</sub> into the PC. CPU is halted.                                                                                                    |

| 8   | INTREQ          | L               | Peripheral device interrupt request.                                                                                                                                     |

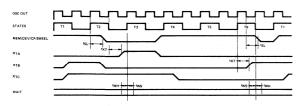

| 9   | XT <sub>A</sub> | н               | External coded minor cycle timing—signifies input transfers to the IM6100.                                                                                               |

| PIN | SYMBOL          | ACTIVE<br>LEVEL                     | DESCRIPTION                                                                                                                                                                                   |

|-----|-----------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | LXMAR           | н                                   | The Load External Address Register is used to store memory and peripheral address externally.                                                                                                 |

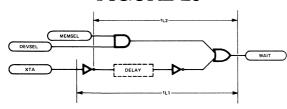

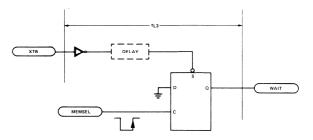

| 11  | WAIT            | L                                   | Indicates that peripherals or external memory is not ready to transfer data. The CPU state gets extended as long as WAIT is active. The CPU is in the lowest power state with clocks running. |

| 12  | XΤ <sub>B</sub> | Н                                   | External coded minor cycle timing—<br>signifies output transfers from the<br>IM6100.                                                                                                          |

| 13  | XT <sub>c</sub> | Н                                   | External coded minor cycle timing—<br>used in conjunction with the Select Lines<br>to specify read or write operations.                                                                       |

| 14  | OSC OUT         |                                     | Crystal input to generate the internal timing (also external clock input).                                                                                                                    |

| 15  | OSC IN          | (12.20) (12.24 × 12.5 VIS.) (14.00) | See Pin 14—OSC OUT (also external clock ground)                                                                                                                                               |

| 16  | DΧ <sub>o</sub> |                                     | DataX—multiplexed data in, data out and address lines.                                                                                                                                        |

| 17  | DX,             |                                     | See Pin 16DX <sub>0</sub> .                                                                                                                                                                   |

| 18  | DX <sub>2</sub> |                                     | See Pin 16—DX <sub>o</sub> .                                                                                                                                                                  |

| 19  | DX₃             |                                     | See Pin 16—DX <sub>o</sub> .                                                                                                                                                                  |

| 20  | DX <sub>4</sub> |                                     | See Pin 16—DX <sub>o</sub> .                                                                                                                                                                  |

| PIN | SYMBOL           | ACTIVE<br>LEVEL                                  | DESCRIPTION                                                                                                                                                                                          |

|-----|------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | DX <sub>5</sub>  |                                                  | See Pin 16DX <sub>o</sub> .                                                                                                                                                                          |

| 22  | $DX_6$           |                                                  | See Pin 16—DX <sub>0</sub> .                                                                                                                                                                         |

| 23  | DX <sub>7</sub>  |                                                  | See Pin 16—DX <sub>0</sub> .                                                                                                                                                                         |

| 24  | DX <sub>8</sub>  | March 19 - 0 - 0 - 0 - 1 - 1 - 1 - 1 - 1 - 1 - 1 | See Pin 16—DX <sub>0</sub> .                                                                                                                                                                         |

| 25  | DX,              |                                                  | See Pin 16-DX <sub>0</sub> .                                                                                                                                                                         |

| 26  | GND              |                                                  | Ground                                                                                                                                                                                               |

| 27  | DX <sub>10</sub> |                                                  | See Pin 16—DX <sub>o</sub> .                                                                                                                                                                         |

| 28  | DX <sub>11</sub> |                                                  | See Pin 16—DX <sub>o</sub> .                                                                                                                                                                         |

| 29  | LINK             | н                                                | Link flip flop.                                                                                                                                                                                      |

| 30  | DEVSEL           | L                                                | Device Select for I/O transfers.                                                                                                                                                                     |

| 31  | SWSEL            | L<br>Marie                                       | Switch Register Select for the OR THE SWITCH REGISTER INSTRUCTION (OSR). OSR is a Group 2 Operate Instruction which reads a 12 bit external switch register and OR's it with the contents of the AC. |

| 32  | C <sub>o</sub>   | L                                                | Control line inputs from the peripheral device during an I/O transfer (Table 5).                                                                                                                     |

| PIN | SYMBOL         | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|-----|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33  | C,             | L               | See Pin 32—Co.                                                                                                                                                                                                                                                                                             |

| 34  | C <sub>2</sub> | L               | See Pin 32—Co.                                                                                                                                                                                                                                                                                             |

| 35  | SKP            | L               | Skips the next sequential instruction if active during an I/O instruction.                                                                                                                                                                                                                                 |

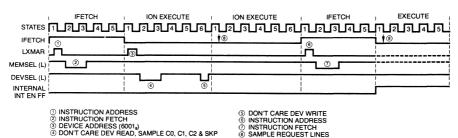

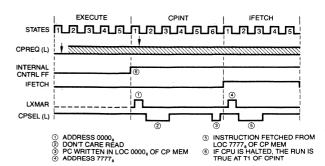

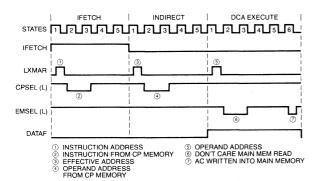

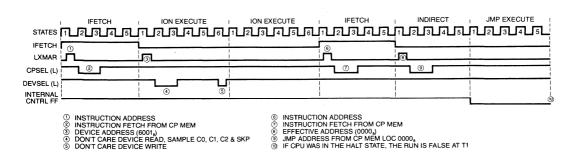

| 36  | IFETCH         | H               | Instruction Fetch Cycle                                                                                                                                                                                                                                                                                    |

| 37  | MEMSEL         | L               | Memory Select for memory transfers.                                                                                                                                                                                                                                                                        |

| 38  | CPSEL          | L               | The Control Panel Memory Select be-<br>comes active, instead of the MEMSEL,<br>for control panel routines. Signal may be<br>used to distinguish between control<br>panel and main memories.                                                                                                                |

| 39  | INTGNT         | н               | Peripheral device Interrupt Grant                                                                                                                                                                                                                                                                          |

| 40  | DATAF          | н               | Data Field pin indicates the execute phase of indirectly addressed AND, TAD, ISZ and DCA instructions so that the data transfers are controlled by the Data Field, DF, and not the Instruction Field, IF, if Extended Memory Control hardware is used to extend the addressing space from 4K to 32K words. |

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage

IM6100/C +4.0V to +7.0V IM6100A +4.0V to 11.0V

Storage Temperature Range

nput or Output Voltage Applied GND - 0.3V to VCC +0.3V -65°C to +150°C Operating Temperature Range

Commercial Industrial Military

$0^{\circ}$ C to  $+70^{\circ}$ C -40°C to +85°C -55°C to +125°C

**>C CHARACTERISTICS**  $V_{cc} = 5.0V \pm 10\%$  (IM6100),  $10.0V \pm 10\%$  (IM6100A),  $T_A =$  Commercial, Industrial or Military

| PARAMETER                  | SYMBOL                              | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TYP             | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UNITS    |

|----------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

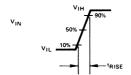

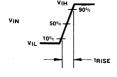

| Logical "1" Input Voltage  | V <sub>IH</sub>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70% V <sub>cc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ٧        |

| Logical "0" Input Voltage  | V <sub>IL</sub>                     | (U.C. 1916, et al. 1) and Lindle (China Sina China Arid Serving Magazine Statistical Service Statistical Service Servi | - I was to the contract of the |                 | 20%V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V        |

| Input Leakage              |                                     | OV ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4               | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | μΑ       |

| Logical "1" Output Voltage | I <sub>IL</sub><br>V <sub>OH2</sub> | I <sub>out</sub> =0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>cc</sub> -0.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V        |

| Logical "1" Output Voltage | V <sub>OH1</sub>                    | I <sub>OH</sub> = -0.2mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Library Company | and the second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>V</b> |

| Logical "0" Output Voltage | Vol2                                | I <sub>out</sub> =0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | GND +0.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V        |

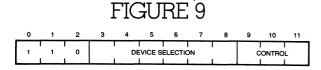

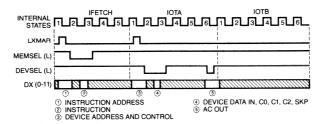

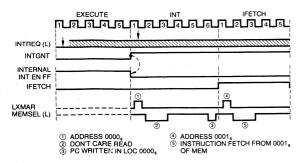

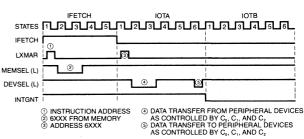

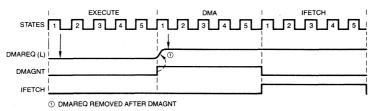

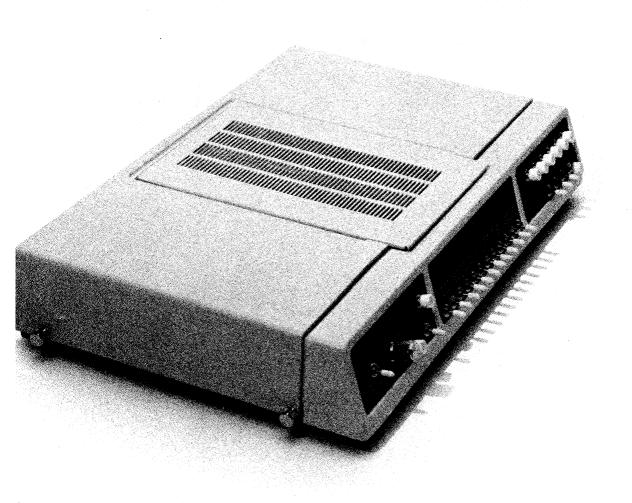

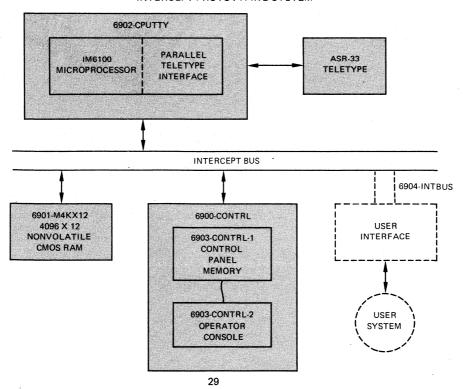

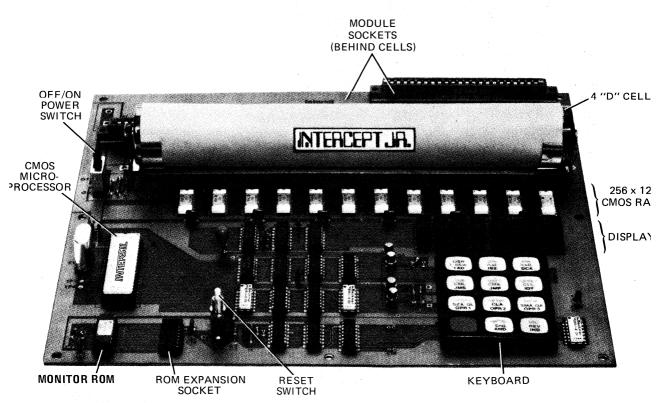

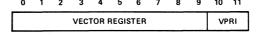

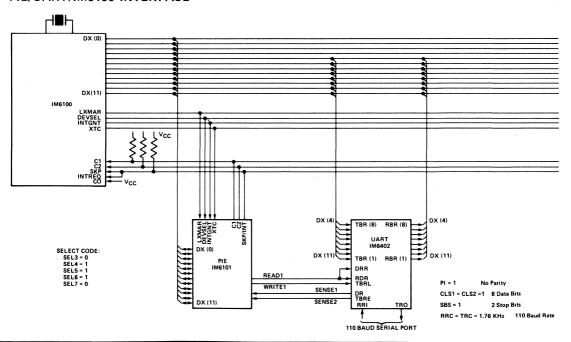

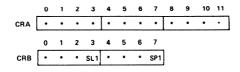

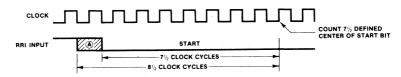

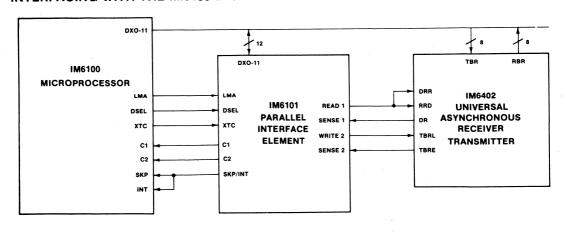

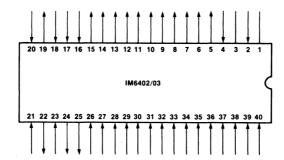

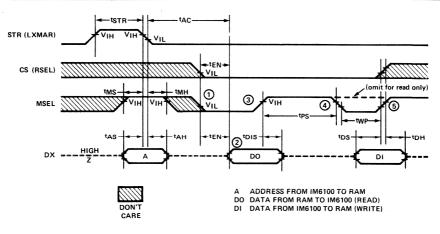

| Logical "0" Output Voltage | V <sub>OL1</sub>                    | I <sub>oL</sub> =1.6 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 0.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V        |